Fraunhofer-Institut für Siliziumtechnologie ISIT

Director Prof. Dr. Wolfgang Benecke

Deputy directors Dr. Wolfgang Windbracke Prof. Dr. Bernhard Wagner

Fraunhoferstraße 1 D-25524 Itzehoe

Phone +49 (0) 4821/17-0 Fax +49 (0) 4821/17-4250

Certified acc. EN ISO 9001:2008

Dr.-lng. Thomas Knieling Direct: +49 (0) 4821/17–4605 Fax: +49 (0) 4821/17-4690

thomas.knieling@isit.fraunhofer.de www.isit.fraunhofer.de

Report

## Reliability testing and stressing of soldered components on PCB

Project No.: 396848

Client: Ovation Products

Mr. Marius Popitiu 3864 Courtney Street

Suite 240A

Bethlehem, PA, 18017

**USA**

Purchase Order No.: 84267C (06/02/2014), ordered by DEK International

Itzehoe, June 3<sup>rd</sup> 2014

i.A. Dr.-Ing. Thomas Knieling

i.A. Dr. Max Poech

## 1. Background & task

During the PCB assembling process the customer employs an array consisting of support stamps equally spaced by about 3 cm to support the PCB during component assembly. In this report this setup is further called Grid-Lok<sup>TM</sup>.

With this analysis the customer wants to prove that the electronic components will not be damaged while supported by a Grid-Lok<sup>TM</sup> stamp either when supported on the components centers or, where applicable, on the components edges. Thus, the mechanical impact of rubber-coated supporting stamps will be analyzed.

## 2. Analysis steps

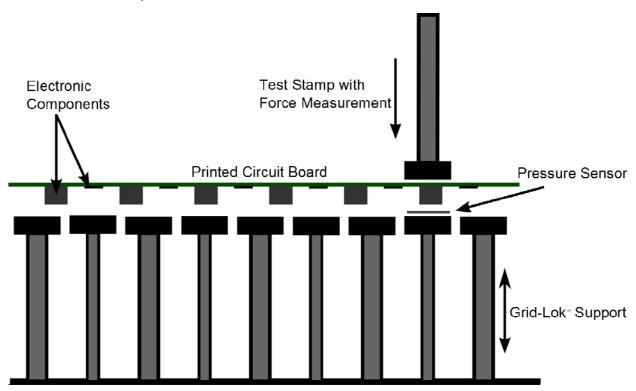

Experimental work was done according to ISIT proven methods. Namely optical microscopy, X-ray analysis and electrical testing by a digital multimeter were used. The test setup for providing mechanical loads on the not-assembled PCB backside, supported by the Grid-Lok<sup>TM</sup> was realized at the ISIT universal testing machine. In fig. 1 the setup is shown schematically.

Fig. 1: Setup scheme for PCB testing.

Before testing the PCB is only hold by the Grid-Lok<sup>TM</sup>, during testing it is clamped only by the holding force between upper load stamp and the Grid-Lok<sup>TM</sup> support. The Grid-Lok<sup>TM</sup> is mounted on a rigid support of the drawing machine. The upper load force, acting on the board backside, is measured by a calibrated force measurement gauge mounted between the test stamp holder and the traverse of the universal testing machine. Its measurement accuracy is at least  $\pm$ 1 mN.

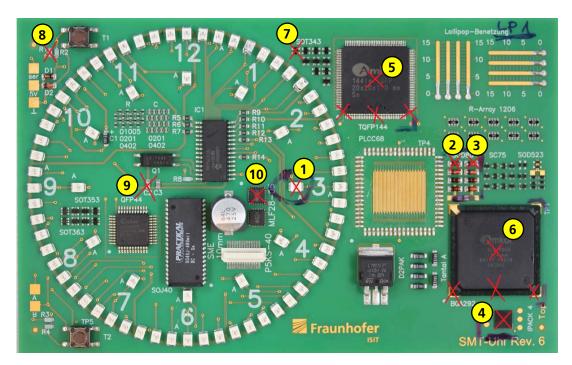

As test samples five already assembled and lead-free soldered ISIT PCB clock boards (fig. 2) were chosen. On these boards only the front sides are assembled.

Fig. 2: Test board (160 mm x 100 mm) with lead-free soldered parts. The red cross markers describe the load test positions, component numbers are marked by yellow circles.

For bigger parts like the BGA and the QFP more than one test position is assigned. For smaller parts an accurate stamp positioning only for the part centers is granted, so only these particular test positions are selected in these cases. Tab. 1 explains in detail the load test positions on different components on each board. As reference the lower board edge in fig. 2 is designated.

| Component # | Description                          | Load positions tested                         |

|-------------|--------------------------------------|-----------------------------------------------|

| 1           | LED A (plastic housing)              | Center                                        |

| 2           | SOD80, 1 (glass diode)               | Center                                        |

| 3           | SOD80, 2 (glass diode)               | Center                                        |

| 4           | IPACK (bare die, soldered with μBGA) | Center                                        |

| 5           | BGA (ball grid array)                | Center, lower center, lower left, lower right |

| 6           | TQFP (quad flat package)             | Center, lower center, lower left, lower right |

| 7           | SOT343 (transistor)                  | Center                                        |

| 8           | Ceramic resistor R1                  | Center                                        |

| 9           | Ceramic capacitor C2                 | Center                                        |

| 10          | MLF                                  | Center                                        |

*Tab. 1*: Designated component numbers, descriptions and their loading regions (see also fig. 2 as reference).

The **basic idea of this analysis** is to measure the load fraction acting on each electronic component 1-10 assembled on the back PCB side, directly positioned below the load stamp and supported itself by a rubber-capped Grid-Lok<sup>TM</sup> stamp (see fig. 1). The rest of the board is also supported by the Grid-Lok<sup>TM</sup> so that the load from above is distributed between the Grid-Lok<sup>TM</sup> stamps below. From this it is already reasonable to think that the electronic component to be tested, which is supported by only one Grid-Lok<sup>TM</sup> stamp, will only receive a minor fraction of this load.

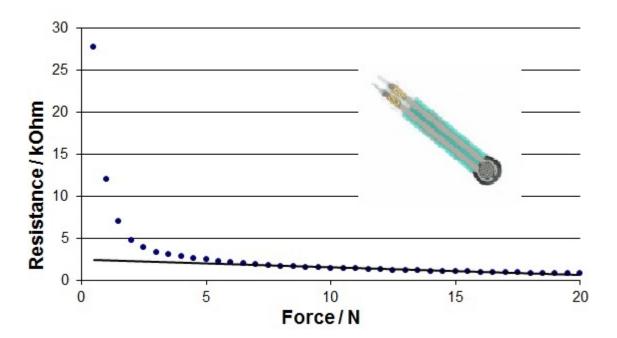

For measuring this load fraction we use a commercially available foil pressure sensor (Interlink, type FSR-400) with resistive measurement principle. This foil sensor is clamped between the Grid-Lok<sup>TM</sup> stamp and the part to be tested. Since the foil sensor shows some hysteresis and drift effects, it is calibrated once before and three times during each measurement, respectively, directly on the universal testing machine (without PCB on a flat rubber support). A typical calibration curve of the foil pressure sensor is shown in fig. 3.

Fig. 3: Typical force-resistance characteristics of a Livelink FSR-400 foil pressure sensor. The inset shows a picture of such a sensor roughly in real dimensions.

The sensor shows linear characteristics only for higher force values. However, forces to be measured here are in the range of 5 N - 20 N, so this sensor is suited for this application.

Each PCB was loaded with a force of 20 N which is 10 times higher than a placement machine would typically do. It is also 1.5-2 times higher than a stencil printer would typically act as. For relevant results, we have chosen to run the experiment beyond extreme conditions like these.

Each loading was done with the same stamps, each capped with the same rubber cap. Damages in the rubber were not observed during test and thus kept for the whole course of measurements.

The status of each tested component was documented before and after testing by

- a) Visual inspection by microscopy

- b) Inspection by Xray radiography (2D)

Since there was no visible effect observed during loading, the analysis by video camera was omitted after doing some observations during different loadings with an inspection microscope.

For random samples electrical functions were tested with a digital multimeter by acquiring an electrical signal (LED: Electrical conductivity, CSP; Daisy chain).

## 3. Results

The documentation containing microscopy and X-ray pictures of each component before and after testing can be seen in the Appendix 1.

Since the whole picture documentation contains 662 single pictures and drawings it is split into five separate parts. Each part has its own caption PCB 1....5 and thus shows the results of one of the named boards. Each report is similarly organized: At first and before loading each component, it's solder joints and - were applicable - the internal structures have been inspected one after another by microscopy from different angles as well as by 2D X-ray analysis according to the list in table 1. After loading the same documentation has been conducted again for each part. The documentation of PCB 5 contains fewer pictures than the other documents. This is due to that this PCB contains an older clock where also fewer components have been assembled.

For all samples tested no visible or remarkable damage has been observed, neither on/in the components nor the at solder joints. Moreover the random electrically tested components show no functional damage at all.

Table 2 in Appendix 2 lists the measured force fractions  $F_{frac}$  for all tested components during the maximum load of  $F_{max}$ = 20 N. It is obvious that especially the small parts do not experience forces higher than 5 N - 8 N. For the bigger components these forces are somewhat higher, which can be attributed to their higher lateral dimensions and their higher area stiffness.

From these results the following conclusions can be drawn:

- 1. Grid-Lok<sup>™</sup> offers robust PCB support and will not damage components or solder joints during the stencil printing and placement processes.

- 2. Grid-Lok<sup>™</sup> soft caps provide additional gentle component support, delivering the effect of a shock absorber during the stencil printing and placement processes. According to the study's measurements, if a force larger than 8-10 Newton is applied, the Grid-Lok pins will collapse.

- 3. Grid-Lok<sup>™</sup> prevents bending of the PCB during the printing and placement processes, which eliminates any opportunity for stress or strain on the components and solder joints as well as PCB vibration.